1. MOSFET : Physical View

우리가 원하는 combinational device는 noise margin을 갖고, VTC인 gain > 1, nonlinearity를 만족해야 한다.

또한, 싸고 크기가 작아야 하며 추가적인 power의 공급없이도 voltage를 유지할 수 있어야 한다. 이러한 combinational device를 조합하여 유용한 기능을 만들 수 있어야 한다.

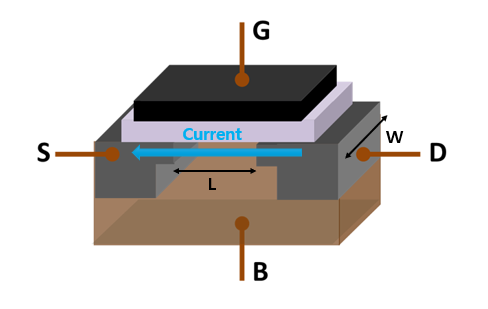

MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor) 이란, 4개의 terminal을 가진 voltage-controlled switch이다. 각각의 terminal은 Gate, Bulk, Source, Drain이다. 기본적으로 MOSFET의 크기는 나노미터 단위로 매우매우 작으며, Moore의 법칙에 따라 계속해서 크기를 줄이며 IC(Integrated Circuit)에 더 많이 집어넣어 성능을 높여왔다.

Bulk는 그 위에 IC가 지어지는 기반(substrate)이다. 처음에는 얇은 wafer of silicon crystal이며, conductivity를 만들기 위해 붕소(Boron)와 같은 불순물(impurities)이 첨가하여 doped silicon으로 만든다. silicon은 최외곽 전자가 4개이고, boron은 최외곽전자가 3개이므로, octet 규칙에 의해 결합시 1개의 전자가 비게 되고, 이로 인해 전자 1개를 받아들일 수 있는 acceptor의 상태가 된다. 이러한 특성을 갖는 doped silicon을 p-type semiconductor라고 한다.

이러한 Bulk와 절연하기 위한 electrical insulator에는 silicon oxide (SiO2) 를 사용하는데, 일반적으로는 이 두께는 중요하지 않지만, gate와 bulk 를 구분하기 위해 사이에 들어가는 insulator는 gate내부의 charge에 의한 electric field가 bulk에 영향을 미칠 수 있을 정도로 얇아야 한다. 이러한 구조는 gate, bulk, insulator로 구성된 Capacitor이 된다.

Gate는 주로 polycrystalline silcon으로 이루어진 conductor이다. 사이의 insulator가 매우 얇으므로, Gate의 voltage 변화는 bulk에 직접적으로 전기적 변화를 야기한다. 초기의 gate는 metal로 이루어져있었고, MOS(metal-oxide-semiconductor)라는 이름도 이러한 구조에서 왔다.

Source, Drain은 substrate에 인(phosphorous)과 같은 전자를 제공할 수 있는 impurities을 주입하여, 해당지역을 n-type semiconductor로 만든 곳이다. 두 곳은 물리적으로는 완전히 동일하다.

2. MOSFET : Electrical view

1) Gate, Bulk, Source, Drain

MOSFET의 동작은 4개의 terminal(Gate, Bulk, Source, Drain)의 voltage에 의해 결정되며, 각각의 terminal은 channel 영역에 electric field를 생성하는 conductor와 연결되어 있다.

Source, Drain은 diffusion terminal로, 둘 중 high voltage를 갖는 것을 drain, low voltage를 갖는 것을 source로 부른다.

따라서, current는 항상 drain에서 source로 흐른다.

Bulk는 GND에 연결되어 voltage가 항상 Source/Drain의 voltage보다 작거나 같은 상태로 유지된다.

2) $ V_{GS} $ > threshold voltage

MOSFET은 Gate voltage $V_G$ 에서 Source voltage $V_S$ 를 뺀 값인 $V_{GS}$ 에 의해 control된다.

MOSFET에는 threshold voltage인 $V_{TH}$ 가 존재하는데, $V_{GS} < V_{TH}$ 일 때 non-conducting (open)이라고 한다. (Switch가 off되어 전류가 흐르지 않는 것)

Source, Drain이 Bulk와 접합하는 위치는 n-type 과 p-type semiconductor가 서로 만나는 곳으로 depletion region이라고 한다. n-type이 전자를 제공하고, p-type이 전자를 받아서 charge가 거의 없는 구간이며, 사이에서 전기적으로 insulation역할을 한다. 이러한 depletion region의 두께는 source/drain과 bulk의 voltage 차이가 커질 수록 증가한다.

$V_{GS}$ 가 커질 수록, Gate에는 더 많은 postive charge가 모이고, bulk의 electron을 끄는 electric field를 생성한다.

$V_{GS}$ 가 threshold voltage를 넘어갈 때, substrate의 atom에 묶여있는 electron이 valence band에서 conduction band로 이동한다. 이렇게 되면 electron은 atom의 속박에서 벗어나 자유롭게 움직일 수 있게 되어, Electron이 Gate와 Bulk사이의 silicon oxide (SiO2) 아래에 모여 depletion region을 형성시킨다(p-type의 정공이 채워지며 중성이됨). Electron이 더 모이면, 최종적으로 n-type으로 inversion 되고, 이렇게 형성된 inversion layer라고 불리는, conducting n-type channel 을 통해 source에서 drain으로 전자가 이동하게 된다.

3) Increasing $ V_{DS} $

$V_{DS}$ 는 Drain voltage $V_D$ 에서 Source voltage $V_S$ 를 뺀 값이며, $ V_{GS} > V_{TH}, V_{DS} < V_{GS} - V_{TH}$ 일 때 Ohm's law에 의해 channel을 통해 흐르는 current $I_{DS} = V_{DS} / R$ 이 성립한다. 이 때 R은 유효저항이다.

하지만, $ V_{GS} > V_{TH}, V_{DS} > V_{GS} - V_{TH}$ 일 때는, $V_{DS}$ 가 증가할수록 drain쪽의 depletion layer가 점점 두꺼워져 drain쪽의 channel을 끊는 pinch-off 지점이 생겨난다. 이에 따라, $V_{DS}$ 증가에 따른 $I_{DS}$ 증가폭은 제한된다(channel이 끊어져도 drain과 source사이의 electric field가 강하다면 depletion region을 넘어서 electron이 이동할 수 있으므로 전류가 조금씩 증가할 수 있음).

이후에도 $V_{DS}$ 를 계속 올리게 되면 이러한 pinch-off 지점이 source쪽으로 이동하게 되고, channel의 length가 짧아지게 된다. 여전히 강한 electric field에 의해 전류가 흐를 수는 있지만 $V_{DS}$ 증가에 따른 $I_{DS}$ 증가폭은 제한된다.

지금까지 우리가 본 MOSFET은 NFET으로, Bulk가 p-type이고 Source/Drain이 n-type이었다.

반대로, Bulk가 n-type이고 Source/Drain이 p-type인 것을 PFET이라고 부른다.

NFET의 switch on은 PFET의 switch off로 동작하게 된다. 따라서 CMOS에서 complementary는 이러한 두가지 type의 MOSFET을 의미한다.

'프로그래밍 > Computer Structure' 카테고리의 다른 글

| 5. Combinational logic (0) | 2024.11.18 |

|---|---|

| 4. CMOS(Complementary Metal-Oxide-Semiconductor) - 2 (0) | 2024.11.12 |

| 2. Digital Abstraction (1) | 2024.10.19 |

| 1. Basics of information (0) | 2024.10.09 |